Solved 23) The feasible region in the diagram below is - Chegg

Question: 23) The feasible region in the diagram below is consistent with which one of the following constraints? Feasible region X1 20 A) 8X1 + 4X2 < 160 B) 8X1 + 4X2 > 160 C) 4X1 …

Using the assumptions above, determine the transistor - Chegg

Here is a summary of these assumptions: Gate/Functional Transistor Propagation Delay Block Count 300 ps 8x1 mux 500 ps 4x1 mux 40 90 full adder 70 300 ps (inputs to sum output) 200 …

Solved Linear Algebra - Homework 2 Find the inverses of the

Use the inverse found in Exercise 1 to solve the system 8x1 + 6x2 = 2 5x1 + 4x2 = -1 6. Use the inverse found in Exercise 3 to solve the system 8x1 + 5x2 = -9 -7xı – 5x2 = 11 7.

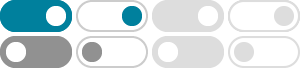

Solved Implement 8 x 1 Digital Multiplexer (MUX), 8 x 1 MUX

The select lines are used to select any one of eight inputs. 10 11 12 out 13 14 15 8x1 MUX 16 Select lines S2 si SO 0 0 0 0 0 1 0 1 0 1 1 0 1 0 1 1 1 1 1 Output Out 10 11 12 13 14 15 16 17 …

Solved Consider the following set of | Chegg.com

Question: Consider the following set of equations: 40=5x3+2x110−x2=x34x2+8x1=2140=5x3+2x110-x2=x34x2+8x1=21 NOTE: This is a multi …

Solved You must design a bus to transfer data between eight

Question: You must design a bus to transfer data between eight 16-bit registers. All eight can be a source; all eight can be a destination. First, design the bus using muxes. Select how many of …

Solved An 8x1 multiplexer has inputs A,B, and C connected to

Question: An 8x1 multiplexer has inputs A,B, and C connected to the selection inputs S2, S1, and S0, respectively. The data inputs I0 through I7 are as follows: I1=I2=I7=0; I3=I5=1; I0=I4=D; …

Solved 7. What is the output function F for the 8x1 | Chegg.com

Here’s how to approach this question Consider that an 8x1 multiplexer is a type of logic circuit with eight input lines, one output line, and three selection inputs, which serves to select one of …

Solved Q19. The feasible region in the diagram below - Chegg

Q19. The feasible region in the diagram below is consistent with which one of the following constraints? A) 8X1 - 4X2 ≤ 160 B) 8X1 + 4X2 ≤ 160 C) 4X1 + 8X2 ≤ 160 D) 4X1 - 8X2 ≤ 160 …

Solved Design a circuit to implement a 3-bit even parity - Chegg

Question: Design a circuit to implement a 3-bit even parity generator using a (8X1) Mux and a (3X8) decoder